JESD204A Page 1 of 2

Home > Products > Intellectual Property > Lattice IP Cores > JESD204A IP Core

# **JESD204A IP Core**

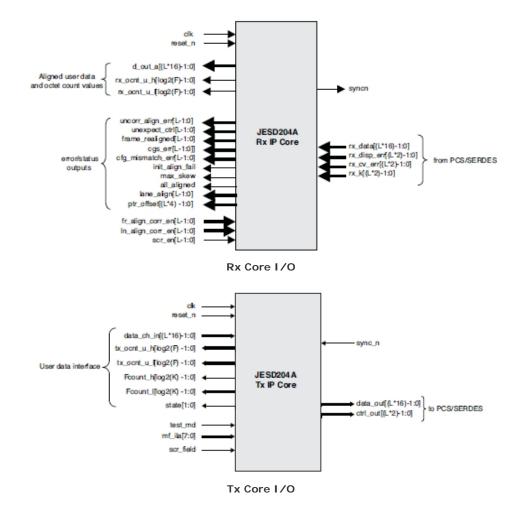

**JEDEC Standard No. 204A (JESD204A)** describes a serialized interface between data converters and logic devices. It contains the information necessary to allow designers to implement devices which can communicate with other devices that are compliant with the standard. Lattice's JESD204A IP Core offerings support both an Rx core (ADC to FPGA direction) and/or a Tx core (FPGA to DAC direction). The Rx and Tx cores can each be generated separately and with different parameters.

#### **Features**

Compliant with JEDEC Standard No. 204A (JESD204A) April 2008

Rx core performs lane alignment buffering / detection / monitoring and correction

Rx core performs frame alignment detection / monitoring and octet reconstruction

Rx core performs user-enabled descrambling

Rx core recovers link configuration parameters during initial lane synchronization and compares them to userselected parameters to generate a configuration mismatch error

Tx core performs user-enabled scrambling

Tx core generates initial lane alignment sequence

Tx core performs alignment character generation

Tx core sources link configuration data with user selected parameter values during initial lane synchronization sequence

Page 2 of 2 JESD204A

#### **Performance and Resource Utilization**

## LatticeECP3<sup>1</sup>

| Configuration | SLICEs | LUTs | Registers | EBRs | f <sub>MAX</sub> (MHz) |

|---------------|--------|------|-----------|------|------------------------|

| Config 1 - Rx | 780    | 1012 | 761       | 0    | 125 <sup>2</sup>       |

| Config 2 - Tx | 337    | 483  | 342       | 0    | 125 <sup>2</sup>       |

<sup>1.</sup> Performance and utilization data target an LFE3-70EA-6FN672C device using Lattice Diamond 1.1 and Synplify Pro for Lattice D-2010.03LSP1 software. Performance may vary when using a different software version or targeting a different device density or speed grade within the LatticeECP3 family.

2. Fmax shown is for 2-lane configuration operating at 2.5 Gbaud using a -6 speed grade device. Higher line rates may require faster speed

### **Ordering Information**

**Family Part Number** LatticeECP3 JESD-204A-E3-U

IP Version: 1.1

Evaluate: To download a full evaluation version of this IP, go to the IPexpress tool and click the IP Server button in the toolbar. All LatticeCORE IP cores and modules available for download will be visible. For more information on

viewing/downloading IP please read the IP Express Quick Start Guide.

Purchase: To find out how to purchase the IP Core, please contact your local Lattice Sales Office.